# TGEN6310&10B&08&04&02 Product Brief

### 1. Description

The TGEN63xx series(TGEN6310/ TGEN6310B/ TGEN6308/ TGEN6304/ TGEN6302) are highperformance and low-jitter clock generator which integrates two any-frequency PLLs for applications that needs to meet PCIE specification or other scenarios. The ultra-low output clock jitter of TGEN63xx series clock generator provides more jitter margin in increasingly complex system, particularly HPC, Storage service, Data Center and Compute Server.

External Crystal(XTAL) or Crystal-Oscillator(XO) provides reference clock which is stable and lowjitter for built-in PLLS.The built-in PLLs can be configured or operate in integral multiplier or fractional multiplier mode independently, as well as Spread-Spectrum-Clock(SSC). Internal integral divider degrade the clock from PLL to a expected frequency, and deliver it to clock output driver. The TGEN63xx series support seven modes of outputs level described in corresponding section. Users can program TGEN63xx easily with GUI to generate any frequency. Factory preprogrammed are also available based on integrated NVM.

# 2. Applications

- Data Center

- X86 / Arm Server

- Automotive Electronics

### 3. Key Features

- PCIe Gen6 Common Clock(CC) 20fs RMS

- PCIe Gen5 Common Clock(CC) 80fs RMS

- Support PCIe CC/SRIS/SRNS clock architecture

- Highly Configurable Spread Spectrum Clock(SSC)

- ♦ Modulation Depth: 0 5000ppm

- ♦ Modulation Range: 30 33kHz

- Spread Mode: Up or Down or Center

Spread

- Reference Clock input frequency range

- ♦ Crystal: 25 54MHz

- Single-Ended and Differential: 10 -100MHz

- Supported Output Mode

- ♦ Single-Ended: LVCMOS

- ♦ Differential: LVDS, LVPECL, CML, HCSL

- Output Clock frequency range

- ♦ Single-Ended: 10 250MHz

- ♦ Differential: 10 1200MHz(HCSL: 10 400MHz)

- Wide Power Supply range

- ♦ VDD&VDDO: 1.8/2.5/3.3V

- ♦ VDDA: 2.5/3.3V

- ♦ Maximal Power Dissipation: 1.3W

- I2C and SPI Serial Interface supported(Maximal frequency for I2C: 400kHz, SPI: 20MHz)

- Support Factory or User Defined One-Time-Program(OTP) based on embedded NVM

- Lead-Free & Fully RoHS Compliant

- Industrial Temperature Support(-40°C~85°C)

- Environment-friendly without Halogen and Antimony

- Package information

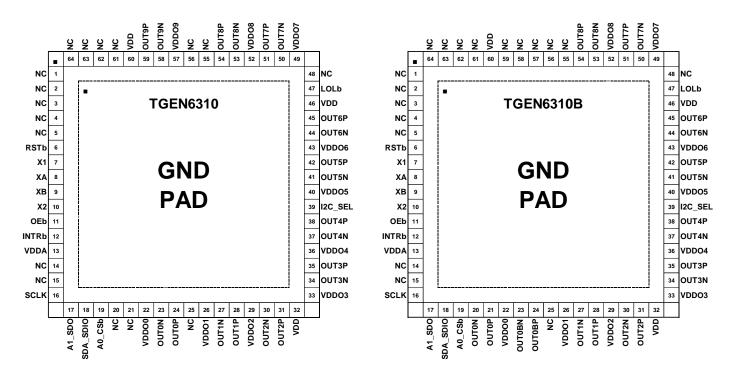

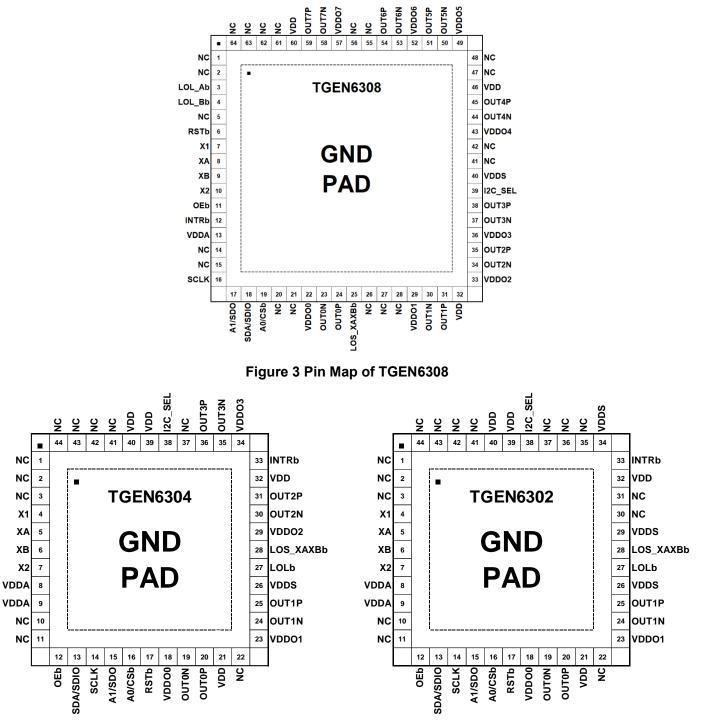

- ♦ TGEN6310/10B/08: 64-QFN 9x9mm package

- ♦ TGEN6304/02: 44-QFN 7x7mm package

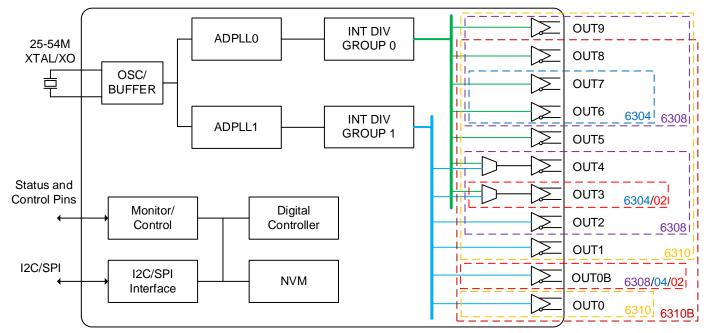

### 4. Functional Diagram

\*All output channel name shown in this Figure is internal alias, not represent for particular model. See Section 4 for more and detailed information.

#### Figure 1 Functional Diagram

#### 5. Pin Maps

Figure 2 Pin Map of TGEN6310 and TGEN6310B

# 6. Pin Descriptions

|          | Pin Number   |               | Dim          |             |                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|----------|--------------|---------------|--------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name | TGEN<br>6310 | TGEN<br>6310B | TGEN<br>6308 | Pin<br>Type | Description                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|          | Clock Input  |               |              |             |                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| ХА       | 8            | 8             | 8            | I           | Reference clock input pins. Connect to external crystal (XTAL) or                                                                                                                                                                                                                                                                                      |  |  |  |

| ХВ       | 9            | 9             | 9            | I           | external reference clock. XA have to connect a external reference clock when using a LVCMOS clock.                                                                                                                                                                                                                                                     |  |  |  |

| X1       | 7            | 7             | 7            | I           | External XTAL shield ground pins. Connect to XTAL GND directly.                                                                                                                                                                                                                                                                                        |  |  |  |

| X2       | 10           | 10            | 10           | I           | When routing PCB trace, the same net of X1, X2 and XTAL GND should be separated from GND plane of PCB. When using external reference clock, these two pins should be left disconnected and DO NOT connect to any net of the PCB.                                                                                                                       |  |  |  |

|          |              |               |              |             | Clock Output                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| OUT0P    | 24           | 21            | 24           | 0           |                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| OUTON    | 23           | 20            | 23           | 0           |                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| OUT0BP   | -            | 24            | -            | 0           |                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| OUT0BN   | -            | 23            | -            | 0           |                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| OUT1P    | 28           | 28            | 31           | 0           |                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| OUT1N    | 27           | 27            | 30           | 0           | 0                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| OUT2P    | 31           | 31            | 35           | 0           |                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| OUT2N    | 30           | 30            | 34           | 0           |                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| OUT3P    | 35           | 35            | 38           | 0           |                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| OUT3N    | 34           | 34            | 37           | 0           | OUTxP/N are the clock out pins. Output mode, swing, common                                                                                                                                                                                                                                                                                             |  |  |  |

| OUT4P    | 38           | 38            | 45           | 0           | mode voltage, output impedance (only in LVCMOS mode) are                                                                                                                                                                                                                                                                                               |  |  |  |

| OUT4N    | 37           | 37            | 44           | 0           | configurable with corresponding register. If any output pin is not in                                                                                                                                                                                                                                                                                  |  |  |  |

| OUT5P    | 42           | 42            | 51           | 0           | use, it should be left unconnected.                                                                                                                                                                                                                                                                                                                    |  |  |  |

| OUT5N    | 41           | 41            | 50           | 0           |                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| OUT6P    | 45           | 45            | 54           | 0           |                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| OUT6N    | 44           | 44            | 53           | 0           |                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| OUT7P    | 51           | 51            | 59           | 0           |                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| OUT7N    | 50           | 50            | 58           | 0           |                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| OUT8P    | 54           | 54            | -            | 0           |                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| OUT8N    | 53           | 53            | -            | 0           |                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| OUT9P    | 59           | -             | -            | 0           |                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| OUT9N    | 58           | -             | -            | 0           |                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|          | 1            |               | S            | erial In    | terface & Control & Status                                                                                                                                                                                                                                                                                                                             |  |  |  |

| RSTb     | 6            | 6             | 6            | I           | Active low. When pulled low, a power-on reset signal will be sent<br>to the device. All volatile memory will be set to the default state and<br>no output is active. Once the external pull-down source is<br>evacuated, the device will load the configuration from NVM(If it's<br>programmed) and return to active state. This pin is pulled-up by a |  |  |  |

|           | Р         | in Numb            | er   | Pin                                     |                                                                                                                    |

|-----------|-----------|--------------------|------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Pin Name  | TGEN      | TGEN   TGEN   TGEN |      | Туре                                    | Description                                                                                                        |

|           | 6310      | 6310B              | 6308 | . , , , , , , , , , , , , , , , , , , , |                                                                                                                    |

|           |           |                    |      |                                         | 20 k $\Omega$ resistor internally and can be left unconnected when not in                                          |

|           |           |                    |      |                                         |                                                                                                                    |

|           |           |                    | 4.4  |                                         | Active low. When pulled low, all outputs are enable. This pin is                                                   |

| OEb       | 11        | 11                 | 11   | I                                       | pulled-up by a 20 k $\Omega$ resistor internally and can be left unconnected when not in use.                      |

|           |           |                    |      |                                         | Active low. When this pin is asserted low, at least one of the device                                              |

| INTRb     | 12        | 12                 | 12   | 0                                       | status occurred. This pin is asserted low, at least one of the device                                              |

|           |           |                    |      |                                         | This pin is the clock input pin for both I2C and SPI modes. When                                                   |

|           |           |                    |      |                                         | in I2C mode, this pin must be pulled-up to VDDA using a resistor                                                   |

| SCLK      | 16        | 16                 | 16   | I                                       | of recommanedly 2.2k $\Omega$ . No pull-up resistor is required in SPI                                             |

|           |           |                    |      |                                         | mode. Pull up or low when this pin is not in use.                                                                  |

|           |           |                    |      |                                         | This is the bidirectional data pin (SDA) for the I2C mode, or the                                                  |

|           |           |                    |      |                                         | bidirectional data pin (SDIO) in the 3-wire SPI mode, or the input                                                 |

| SDA_SDIO  | 18        | 18                 | 10   | I/O                                     | data pin (SDI) in 4-wire SPI mode. When in I2C mode, this pin must                                                 |

| 3DA_3DIO  | 10        | 10                 | 18   | 1/0                                     | be pulled-up using an external resistor of at least 1 k $\Omega.$ No pull-up                                       |

|           |           |                    |      |                                         | resistor is needed when is SPI mode. Pull low when this pin is not                                                 |

|           |           |                    |      |                                         | in use.                                                                                                            |

|           |           |                    |      |                                         | In I2C mode, this pin functions as the A1 address input pin and                                                    |

| A1_SDO    | 17        | 17                 | 17   | I/O                                     | does not have an internal pull-up or pull-down resistor. In 4-wire                                                 |

|           |           |                    |      |                                         | SPI mode this is the serial data output (SDO) pin and drives high                                                  |

|           |           |                    |      |                                         | to the voltage of VDDA.                                                                                            |

|           | A0_CSb 19 | 19                 | 19   | I                                       | This pin functions as the hardware controlled address A0 in I2C                                                    |

| A0_CSb    |           |                    |      |                                         | mode. In SPI mode, this pin functions as the chip select input                                                     |

|           |           |                    |      |                                         | (active low). This pin is internally pulled-up by a ~20 k $\Omega$ resistor                                        |

|           |           |                    |      |                                         | and can be left unconnected when not in use.<br>When pulled high, the device will use I2C as serial interface, and |

|           |           |                    |      |                                         | the address of I2C is determined by the level of pins A1_SDO and                                                   |

| I2C_SEL   | 39        | 39                 | 39   |                                         | A0_CSb.                                                                                                            |

| 120_012   | 00        | 00                 | 00   |                                         | When pulled low, the device will use SPI as serial interface.                                                      |

|           |           |                    |      |                                         | This pin is pulled-up by a 20 k $\Omega$ resistor internaly.                                                       |

|           |           |                    |      |                                         | Active low. When this pin is asserted low, at least one of the PLL                                                 |

| LOLb      | 47        | 47                 | -    | 0                                       | is in state of Loss-Of-Lock. This pin should be left unconnected if                                                |

|           |           |                    |      |                                         | not in use.                                                                                                        |

|           |           |                    | 0    | 0                                       | Active low. When this pin is asserted low, PLL0 is in state of Loss-                                               |

| LOL_Ab    | -         | -                  | 3    | 0                                       | Of-Lock. This pin should be left unconnected if not in use.                                                        |

|           |           |                    | 4    | 0                                       | Active low. When this pin is asserted low, PLL1 is in state of Loss-                                               |

| LOL_Bb    | -         | -                  | 4    | 0                                       | Of-Lock. This pin should be left unconnected if not in use.                                                        |

| LOS_XAXBb | -         | -                  | 25   | 0                                       | Active low. When this pin is asserted low, reference clock from                                                    |

|           |           |                    | 20   |                                         | XA/XB pins is lost. This pin should be left unconnected if not in use.                                             |

|           |           |                    |      |                                         | Power Supply                                                                                                       |

|           | 32        | 32                 | 32   | Р                                       | Power supply for internal PLLs and dividers. This pin is an analog                                                 |

| VDD       | 46        | 46                 | 46   | Р                                       | power supply pin and should be separated from digital power                                                        |

|           | 60        | 60                 | 60   | Р                                       | supply. A 1.0 $\mu F$ and a 0.1 $\mu F$ bypass capacitors should be placed                                         |

|           |           |                    |      |                                         | very closed to each pin recommend.                                                                                 |

| TGEN | 63xx | series |

|------|------|--------|

|------|------|--------|

|          | P              | in Numb | er          |             |                                                                                                                                                                                                                                                                             |  |

|----------|----------------|---------|-------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin Name | TGEN TGEN TGEN |         | Pin<br>Type | Description |                                                                                                                                                                                                                                                                             |  |

|          | 6310           | 6310B   | 6308        | Type        |                                                                                                                                                                                                                                                                             |  |

| VDDA     | 13             | 13      | 13          | Ρ           | Power supply for analog module of reference clock input and internal logic. This pin is an analog power supply pin and should be separated from digital power supply. A 1.0 $\mu$ F and a 0.1 $\mu$ F bypass capacitors should be placed very closed to this pin recommend. |  |

| VDDO0    | 22             | 22      | 22          | Р           |                                                                                                                                                                                                                                                                             |  |

| VDDO1    | 26             | 26      | 29          | Р           |                                                                                                                                                                                                                                                                             |  |

| VDDO2    | 29             | 29      | 33          | Р           |                                                                                                                                                                                                                                                                             |  |

| VDDO3    | 33             | 33      | 36          | Р           |                                                                                                                                                                                                                                                                             |  |

| VDDO4    | 36             | 36      | 43          | Р           | Power supply for OUTx outputs. Supply voltage in range of 3.3V, 2.5V, 1.8V is supported. Left power supply unconnected if the                                                                                                                                               |  |

| VDDO5    | 40             | 40      | 49          | Р           | output is not in use to minimize power consumption.                                                                                                                                                                                                                         |  |

| VDDO6    | 43             | 43      | 52          | Р           |                                                                                                                                                                                                                                                                             |  |

| VDDO7    | 49             | 49      | 57          | Р           |                                                                                                                                                                                                                                                                             |  |

| VDDO8    | 52             | 52      | -           | Р           |                                                                                                                                                                                                                                                                             |  |

| VDDO9    | 57             | -       | -           | Р           |                                                                                                                                                                                                                                                                             |  |

| VDDS     | -              | -       | 40          | Ρ           | Power supply for LOL_Ab and LOL_Bb outputs. Supply voltage in range of 3.3V, 2.5V, 1.8V is supported. A 1.0 $\mu$ F and a 0.1 $\mu$ F bypass capacitors should be placed very closed to this pin recommend.                                                                 |  |

| GND      |                | EPAD    | 1           | G           | Ground pin for TGEN63xx.                                                                                                                                                                                                                                                    |  |

| Not Used |                |         |             |             |                                                                                                                                                                                                                                                                             |  |

|          | 1              | 1       | 1           | -           |                                                                                                                                                                                                                                                                             |  |

|          | 2              | 2       | 2           | -           |                                                                                                                                                                                                                                                                             |  |

|          | 3              | 3       | 5           | -           |                                                                                                                                                                                                                                                                             |  |

|          | 4              | 4       | 14          | -           |                                                                                                                                                                                                                                                                             |  |

|          | 5              | 5       | 15          | -           |                                                                                                                                                                                                                                                                             |  |

|          | 14             | 14      | 20          | -           |                                                                                                                                                                                                                                                                             |  |

|          | 15             | 15      | 21          | -           |                                                                                                                                                                                                                                                                             |  |

|          | 20             | 25      | 26          | -           |                                                                                                                                                                                                                                                                             |  |

|          | 21             | 48      | 27          | -           |                                                                                                                                                                                                                                                                             |  |

| NC       | 25             | 55      | 28          | -           | TBD                                                                                                                                                                                                                                                                         |  |

|          | 48             | 56      | 41          | -           |                                                                                                                                                                                                                                                                             |  |

|          | 55             | 57      | 42          | -           |                                                                                                                                                                                                                                                                             |  |

|          | 56             | 58      | 47          | -           |                                                                                                                                                                                                                                                                             |  |

|          | 61             | 59      | 48          | -           |                                                                                                                                                                                                                                                                             |  |

|          | 62             | 61      | 55          | -           |                                                                                                                                                                                                                                                                             |  |

|          | 63             | 62      | 56          | -           |                                                                                                                                                                                                                                                                             |  |

|          | 64             | 63      | 61          | -           |                                                                                                                                                                                                                                                                             |  |

|          | -              | 64      | 62          | -           |                                                                                                                                                                                                                                                                             |  |

|          | -              | -       | 63          | -           |                                                                                                                                                                                                                                                                             |  |

|          | -              | -       | 64          | -           |                                                                                                                                                                                                                                                                             |  |

#### Table 2 48-QFN 7x7mm Pin List

|                                     | Pin N | umber |          |                                                                                                                                                                                                                                                                                                                                                                  |  |

|-------------------------------------|-------|-------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin Name                            | TGEN  | TGEN  | Pin Type | Describetion                                                                                                                                                                                                                                                                                                                                                     |  |

|                                     | 6304  | 6302  |          | Clock Input                                                                                                                                                                                                                                                                                                                                                      |  |

| ХА                                  | 5     | 5     |          | Reference clock input pins. Connect to external crtstal(XTAL) or                                                                                                                                                                                                                                                                                                 |  |

| XB                                  | 6     | 6     | · ·      | external reference clock. XA have to connect a external reference                                                                                                                                                                                                                                                                                                |  |

|                                     | 0     | 0     | 1        | clock when using a LVCMOS clock.                                                                                                                                                                                                                                                                                                                                 |  |

| X1                                  | 4     | 4     | I        | External XTAL sheld ground pins. Connect to XTAL GND directly.                                                                                                                                                                                                                                                                                                   |  |

| X2                                  | 7     | 7     | I        | When routing PCB trace, the same net of X1, X2 and XTAL GND should be separated from GND plane of PCB. When using external reference clock, these two pins should be left disconnected and DO NOT connect to any net of the PCB.                                                                                                                                 |  |

|                                     | I     | I     |          | Clock Output                                                                                                                                                                                                                                                                                                                                                     |  |

| OUT0P                               | 20    | 20    | 0        |                                                                                                                                                                                                                                                                                                                                                                  |  |

| OUTON                               | 19    | 19    | 0        |                                                                                                                                                                                                                                                                                                                                                                  |  |

| OUT1P                               | 25    | 25    | 0        | OUTVD/N are the cleak out size. Output mode, output and                                                                                                                                                                                                                                                                                                          |  |

| OUT1N                               | 24    | 24    | 0        | OUTxP/N are the clock out pins. Output mode, swing, common mode voltage, output impedence(only in LVCMOS mode) are configurable                                                                                                                                                                                                                                  |  |

| OUT2P                               | 31    | -     | 0        | with corresponding register. If any output pin is not in use, it should be                                                                                                                                                                                                                                                                                       |  |

| OUT2N                               | 30    | -     | 0        |                                                                                                                                                                                                                                                                                                                                                                  |  |

| OUT3P                               | 36    | _     | 0        |                                                                                                                                                                                                                                                                                                                                                                  |  |

| OUT3N                               | 35    | -     | 0        | _                                                                                                                                                                                                                                                                                                                                                                |  |

| Serial Interface & Control & Status |       |       |          |                                                                                                                                                                                                                                                                                                                                                                  |  |

|                                     |       |       | Jena     | Active low. When pulled low, all outputs are enable. This pin is pulled-                                                                                                                                                                                                                                                                                         |  |

| OEb                                 | 12    | 12    | I        | up by a 20 k $\Omega$ resistor internaly and can be left unconnected when not in use.                                                                                                                                                                                                                                                                            |  |

| SCLK                                | 14    | 14    | I        | This pin is the clock input pin for both I2C and SPI modes. When in I2C mode, this pin must be pulled-up to VDDA using a resistor of recommanedly $2.2k\Omega$ . No pull-up resistor is required in SPI mode. Pull up or low when this pin is not in use.                                                                                                        |  |

| SDA_SDIO                            | 13    | 13    | I/O      | This is the bidirectional data pin (SDA) for the I2C mode, or the bidirectional data pin (SDIO) in the 3-wire SPI mode, or the input data pin (SDI) in 4-wire SPI mode. When in I2C mode, this pin must be pulled-up using an external resistor of at least 1 k $\Omega$ . No pull-up resistor is needed when is SPI mode. Pull low when this pin is not in use. |  |

| A1_SDO                              | 15    | 15    | I/O      | In I2C mode, this pin functions as the A1 address input pin and does<br>not have an internal pull-up or pull-down resistor. In 4-wire SPI mode<br>this is the serial data output (SDO) pin and drives high to the voltage<br>of VDDA.                                                                                                                            |  |

| A0_CSb                              | 16    | 16    | I        | This pin functions as the hardware controlled address A0 in I2C mode.<br>In SPI mode, this pin functions as the chip select input (active low).<br>This pin is internally pulled-up by a ~20 k $\Omega$ resistor and can be left<br>unconnected when not in use.                                                                                                 |  |

| RSTb                                | 17    | 17    | I        | Active low. When pulled low, a power-on reset signal will be sent to<br>the device. All volatile memory will be set to the default state and no<br>output is active. Once the external pull-down source is evacuated, the                                                                                                                                        |  |

www.silicon-innovation-cd.com

|                                                                       | Pin Number                                                          |      |          |                                                                                                                                              |  |

|-----------------------------------------------------------------------|---------------------------------------------------------------------|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin Name TGEN                                                         |                                                                     | TGEN | Pin Type | Describetion                                                                                                                                 |  |

|                                                                       | 6304                                                                | 6302 |          |                                                                                                                                              |  |

|                                                                       |                                                                     |      |          | device will load the configuration from NVM(If it's programmed) and                                                                          |  |

|                                                                       |                                                                     |      |          | return to active state. This pin is pulled-up by a 20 $k\Omega$ resistor internaly                                                           |  |

|                                                                       |                                                                     |      |          | and can be left unconnected when not in use.                                                                                                 |  |

|                                                                       |                                                                     |      |          | Active low. When this pin is asserted low, at least one of the PLL is in                                                                     |  |

| LOLb                                                                  | 27                                                                  | 27   | 0        | state of Loss-Of-Lock. This pin should be left unconnected if not in                                                                         |  |

|                                                                       |                                                                     |      |          | USE.                                                                                                                                         |  |

| LOS_XAXBb                                                             | 28                                                                  | 28   | 0        | Active low. When this pin is asserted low, reference clock from XA/XB                                                                        |  |

|                                                                       |                                                                     |      |          | pins is lost. This pin should be left unconnected if not in use.                                                                             |  |

| INTRb                                                                 | 33                                                                  | 33   | I        | Active low. When this pin is asserted low, at least one of the device                                                                        |  |

|                                                                       |                                                                     |      |          | status occured. This pin should be left unconnected if not in use.<br>When pulled high, the device will use I2C as serial interface, and the |  |

|                                                                       |                                                                     |      |          | address of I2C is determined by the level of pins A1_SDO and                                                                                 |  |

| I2C_SEL                                                               | 38                                                                  | 38   | 1        | A0 CSb.                                                                                                                                      |  |

| 120_0LL                                                               | 50                                                                  |      |          | When pulled low, the device will use SPI as serial interface.                                                                                |  |

|                                                                       |                                                                     |      |          | This pin is pulled-up by a 20 k $\Omega$ resistor internaly.                                                                                 |  |

|                                                                       |                                                                     |      |          | Power Supply                                                                                                                                 |  |

|                                                                       | 21                                                                  | 21   | Р        | Pwer supply for internal PLLs and deviders. This pin is an analog                                                                            |  |

| 3232Ppower supply pin and should b3939PA 1.0 µF and a 0.1 µF bypass c | power supply pin and should be separated from digital power supply. |      |          |                                                                                                                                              |  |

|                                                                       |                                                                     |      | Р        | A 1.0 $\mu$ F and a 0.1 $\mu$ F bypass capacitors should be placed very closed                                                               |  |

|                                                                       | 40                                                                  | 40   | P        | to each pin recommendly.                                                                                                                     |  |

|                                                                       | 8                                                                   | 8    | P        | Power supply for analog module of reference clock input and internal                                                                         |  |

| VDDA                                                                  |                                                                     |      |          | logic. This pin is an analog power supply pin and should be separated                                                                        |  |

|                                                                       | 9                                                                   | 9    | Р        | from digital power supply. A 1.0 $\mu$ F and a 0.1 $\mu$ F bypass capacitors                                                                 |  |

|                                                                       |                                                                     |      |          | should be placed very closed to this pin recommendly.                                                                                        |  |

| VDDO0                                                                 | 18                                                                  | 18   | Р        |                                                                                                                                              |  |

| VDDO1                                                                 | 23                                                                  | 23   | Р        | Power supply for OUTx outputs. Supply voltage in range of 3.3V, 2.5V,                                                                        |  |

| VDDO2                                                                 | 29                                                                  | -    | Р        | 1.8V is supported. Left power supply unconnected if the output is not                                                                        |  |

| VDDO3                                                                 | 33                                                                  | -    | Р        | in use to minimize power consumption.                                                                                                        |  |

|                                                                       | 26                                                                  | 26   | Р        | Power supply for LOL_Ab and LOL_Bb outputs. Supply voltage in                                                                                |  |

| VDDS                                                                  | -                                                                   | 29   | Р        | range of 3.3V, 2.5V, 1.8V is supported. A 1.0 $\mu$ F and a 0.1 $\mu$ F bypass                                                               |  |

|                                                                       | -                                                                   | 34   | Р        | capacitors should be placed very closed to this pin recommendly.                                                                             |  |

| GND                                                                   | EP                                                                  |      | G        | Ground pin for TGEN63xx.                                                                                                                     |  |

|                                                                       |                                                                     |      |          | Not Used                                                                                                                                     |  |

|                                                                       | 1                                                                   | 1    | -        |                                                                                                                                              |  |

|                                                                       | 2                                                                   | 2    | -        |                                                                                                                                              |  |

|                                                                       | 3                                                                   | 3    | -        |                                                                                                                                              |  |

|                                                                       | 10                                                                  | 10   | -        |                                                                                                                                              |  |

| NC                                                                    | 11                                                                  | 10   | -        | TBD                                                                                                                                          |  |

| NC                                                                    | 22                                                                  | 22   |          | שטו                                                                                                                                          |  |

|                                                                       |                                                                     |      | -        |                                                                                                                                              |  |

|                                                                       | 37                                                                  | 30   | -        |                                                                                                                                              |  |

|                                                                       | 41                                                                  | 31   | -        |                                                                                                                                              |  |

|                                                                       | 42                                                                  | 35   | -        |                                                                                                                                              |  |

| <b>TGEN63xx series</b> | TG | EN | 63xx | series |

|------------------------|----|----|------|--------|

|------------------------|----|----|------|--------|

|          | Pin Nu | umber |          |              |

|----------|--------|-------|----------|--------------|

| Pin Name | TGEN   | TGEN  | Pin Type | Describetion |

|          | 6304   | 6302  |          |              |

|          | 43     | 36    | -        |              |

|          | 44     | 37    | -        |              |

|          | -      | 41    | -        |              |

|          | -      | 42    | -        |              |

|          | -      | 43    | -        |              |

|          | -      | 44    | -        |              |