# TUBF0308 Product Brief

## 1. Description

The TBUF0308 is an excellent clock buffer chip. It supports 1.5GHz frequency and 8 outputs with ultra-low delay and jitter. It is mainly used in applications such as low jitter, high-frequency clock / data distribution and level conversion.

The buffer can support input from 3 modes clock sources, such as single-ended clock or differential clock or crystal source.

The TBUF0308 can be allocated to two output group A and B and one LVCMOS output.

Each channel output of A and B banks can be independently programmed to LVPECL, LVDS, HCSL or HIZ mode. The LVCMOS clock output is synchronized with the selected clock and can be enabled or disabled.

The TBUF0308 supports flexible voltage range. Both core voltage and IO voltage support 2.5V or 3.3V power supply.

# 2. Applications

- IT infrastructure (servers, storages)

- 5g communication

- Network system, including switches and routers

- Automotive electronics

## 3. Key Features

- Two inputs support including Single-Ended, Differential and Crystal

- 8 outputs support three modes including LVDS, LVPECL and HCSL

- Up to 1.5GHz Output Frequency for Differential Outputs

- Up to 200MHz Reference Output for LVCMOS

- Ultra-low Measured Jitter

- Low Delay from inputs to outputs channel

- Low Skew between outputs within different banks

- Flexible independent supply voltage of 3.3V/2.5V

- Lead-Free & Fully RoHS Compliant

- Industrial Temperature Support ( -40°C

- ~ 85°C)

- Environment-friendly without Halogen and Antimony

- 40-pin, 6mm x 6mm QFN package

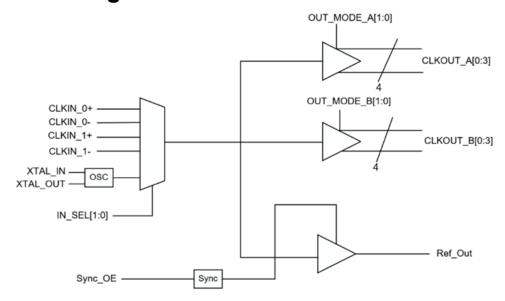

# 4. Functional Diagram

Figure 1 Functional Diagram

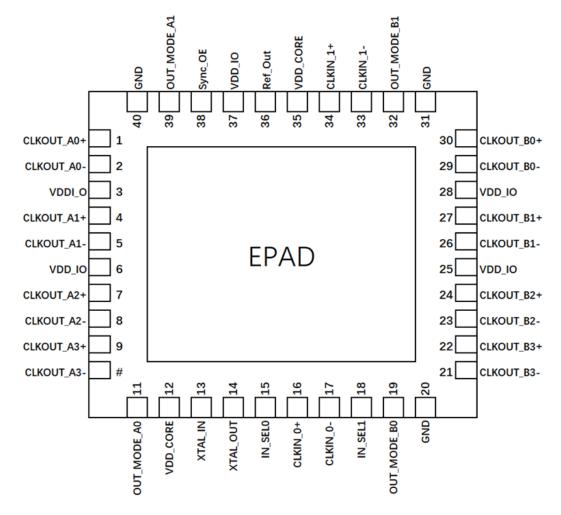

# 5. Pin Maps

Figure 2 Pin Assignment Diagram-QFN40

# 6. Pin Descriptions

#### **Table 1 Pin Descriptions**

| Pin #            | Pin Name    | Туре   | Description                                                                                |

|------------------|-------------|--------|--------------------------------------------------------------------------------------------|

| 1, 2             | CLKOUT_A0+  | Output | Differential clock output P/N of BANK A Channel 0. Can be configured by OUT_MODE_A pins.   |

|                  | CLKOUT_A0-  |        |                                                                                            |

| 4, 5             | CLKOUT_A1+  | Output | Differential clock output P/N of BANK A Channel 1. Can be configured by OUT_MODE_A pins    |

|                  | CLKOUT_A1-  |        |                                                                                            |

| 3, 6, 25, 28, 37 | VDD_IO      | Power  | Power supply pins for Output buffers.                                                      |

| 7, 8             | CLKOUT_A2+  | Output | Differential clock output P/N of BANK A Channel 2.<br>Can be configured by OUT_MODE_A pins |

|                  | CLKOUT_A2-  |        |                                                                                            |

| 9, 10            | CLKOUT_A3+  | Output | Differential clock output P/N of BANK A Channel 3. Can be configured by OUT_MODE_A pins    |

|                  | CLKOUT_A3-  |        |                                                                                            |

| 20, 31, 40       | GND         | Power  | Ground pins.                                                                               |

| 11               | OUT_MODE_A0 | Input  | Pulldown. Bank A output buffer type selection pins. View Table 3 for details.              |

| 39               | OUT_MODE_A1 | Input  |                                                                                            |

| 12, 35           | VDD_CORE    | Power  | Power supply pins for core.                                                                |

| 13               | XTAL_IN     | Input  | Input pin for crystal supporting single ended input                                        |

| 14               | XTAL_OUT    | Output | Output pin for crystal. Leave XTAL_out OPEN if XTAL_in is driven by a single- ended clock. |

| 15, 18           | IN_SEL      | Input  | Pulldown. Clock input selections pins. View Table 2 for details.                           |

| 16               | CLKIN_0+    | Input  | Universal clock input 0, built_in deviation to 0.33VDD_CORE                                |

| 17               | CLKIN_0-    | Input  | Pullup/Pulldown.Reverse reference input 0, built_in deviation to 0.42V <sub>DD_CORE</sub>  |

| 19               | OUT_MODE_B0 | Input  | Pulldown. Bank B output buffer type selection pins. View Table 2 for details.              |

| 32               | OUT_MODE_B1 | Input  |                                                                                            |

| 22, 21           | CLKOUT_B3+  | Output | Differential clock output P/N of BANK B Channel 3. Can be configured by OUT_MODE_B pins.   |

|                  | CLKOUT_B3-  |        |                                                                                            |

| 24, 23           | CLKOUT_B2+  | Output | Differential clock output P/N of BANK B Channel 2. Can be configured by OUT_MODE_B pins.   |

|                  | CLKOUT_B2-  |        |                                                                                            |

| 27, 26           | CLKOUT_B1+  | Output | Differential clock output P/N of BANK B Channel 1. Can be configured by OUT_MODE_B pins.   |

|                  | CLKOUT_B1-  |        |                                                                                            |

| 30, 29           | CLKOUT_B0+  | Output | Differential clock output P/N of BANK B Channel 0. Can be configured by OUT_MODE_B pins.   |

|                  | CLKOUT_B0-  |        |                                                                                            |

| 33               | CLKIN_1-    | Input  | Pullup/Pulldown. Reverse reference input 0, built_in deviation to 0.42V <sub>DD_CORE</sub> |

| 34               | CLKIN_1+    | Input  | Pulldown. Reverse reference input 0, built_in deviation to 0.33V <sub>DD_CORE</sub>        |

| 36               | Ref_OUT     | Output | Reference output, CMOS                                                                     |

| 38               | Sync_OE     | Input  | Pulldown.Synchronous output supports Ref_Out. View Table 4 for details.                    |

| EPAD             | EPAD        | gnd    | Ground pins.                                                                               |