Provide you with enterprise-level interconnection chips

We offer a series of clock generators and buffers with super low jitter and low power consumption to provide you with the clock signals your circuits need and improve the quality and stability of your clock signals, so as to ensure system performance and reliability.

We offer easy-to-use single-end clock buffers with low jitter and low power consumption, which flexibly support single-end, differential, and crystal inputs, and generate multiple LVCMOS clock sources for you to simplify your clock tree design.

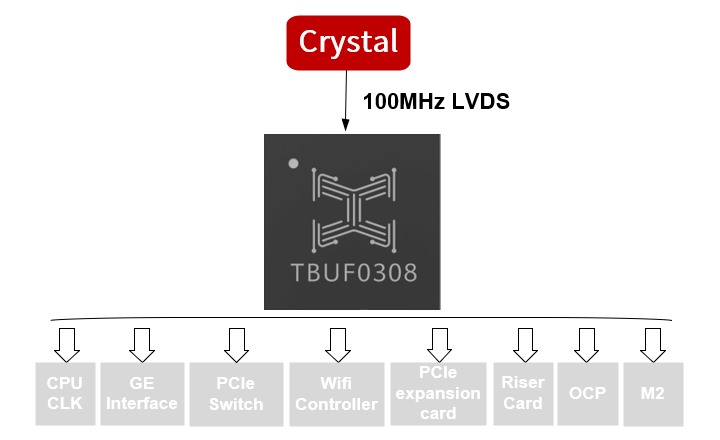

We offer a wide range of differential clock buffer products that flexibly support single-end, differential, and crystal inputs, with features such as low additional jitter performance and low power consumption. With multiple outputs, these products can be flexibly configured for industry-wide output levels such as LVCMOS, LVDS, LVPECL, and HCSL.

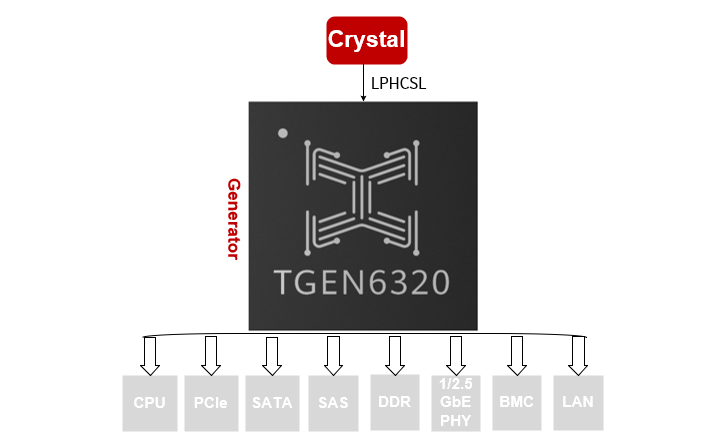

We offer a wide range of clock generators with features such as low jitter, programmability, and spread spectrum, which support PCIe 5.0. It can help you simplify clock tree design, reduce PCB layout space, and reduce clock solution costs in applications such as servers, communications, and industrial control.

| Part .NO | Operating voltage | Input type | Output type | Output frequency(Max) | Additive jitter | Number of output channels | Operating temperature | Package |

| TBUF0210 | 2.5V/3.3V | crystal/single-ended/differential | LVCMOS | 200MHz | <50fs | 10 | -40℃~85℃ | QFN32 |

| TBUF0208 | 2.5V/3.3V | crystal/single-ended/differential | LVCMOS | 200MHz | <50fs | 8 | -40℃~85℃ | QFN32 |

| TBUF0204 | 1.5V/1.8V/2.5V/3.3V | single-ended | LVCMOS | 200MHz | <50fs | 4 | -40℃~85℃ | SOIC8 |

Copyright ? 2000-2023 成都電科星拓科技有限公司 版權(quán)所有 備案編號: 蜀ICP備2022009451號 川公網(wǎng)安備 51019002004893號